高云FPGA开发笔记(二) Gowin软件与基础开发流程详解

一、引言

在上一期笔记中,我们初步认识了高云(GOWIN)FPGA及其应用场景。本期将聚焦于高云官方的FPGA开发软件——Gowin云源软件,并详细介绍其基础软件开发流程,为后续的实战项目打下坚实基础。

二、Gowin云源软件概览

高云FPGA的官方集成开发环境(IDE)是 Gowin云源软件(Gowin YunYuan)。它是一个集设计输入、综合、布局布线、仿真和编程下载于一体的工具链。

- 主要组件:

- Gowin设计软件(核心):包含工程管理、逻辑综合、布局布线、比特流生成等核心功能。

- Gowin综合器:将硬件描述语言(如Verilog HDL、VHDL)或原理图转换为门级网表。

- Gowin布局布线器:将网表映射到目标FPGA芯片的具体逻辑资源上,并完成连线。

- 编程下载工具:生成最终的比特流文件,并通过下载器(如Gowin编程器)将其烧录到FPGA芯片中。

- Gowin在线逻辑分析仪(GLA):一个强大的片上调试工具,无需额外IO引脚即可实时捕获内部信号,极大方便了调试。

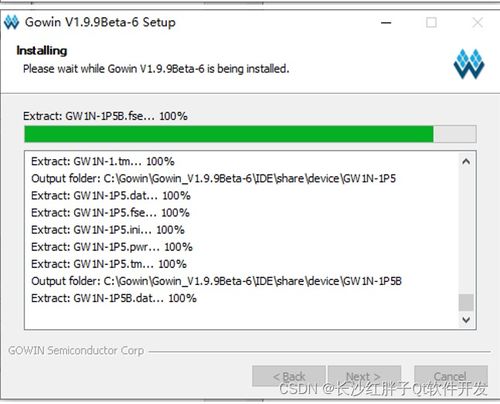

- 软件获取与安装:

- 访问高云半导体官方网站,在“支持”或“下载”页面找到最新版本的Gowin云源软件。

- 安装过程简单,跟随向导即可。安装完成后,首次启动可能需要申请(或已有)免费的License文件进行激活。高云为教育和中小规模设计提供了较为友好的授权策略。

三、高云FPGA基础开发流程

一个完整的FPGA开发周期通常遵循以下步骤,在高云开发环境中也不例外:

第1步:创建新工程

启动Gowin软件,通过“File -> New Project”创建工程。关键设置包括:

- 工程名称与路径:建议使用英文路径。

- 选择器件型号:根据你手中的开发板(如小熊猫系列、GW1N系列等)准确选择FPGA的具体型号(如GW1N-LV4LQ144C6/I5)。

第2步:设计输入

这是将设计构思转化为计算机可识别形式的关键一步,主要有三种方式:

- 硬件描述语言(HDL):最主流的方式。在软件中“新建文件”,选择Verilog或VHDL文件,编写代码描述电路功能。

- 原理图输入:对于小型或直观的组合逻辑,可以通过绘制原理图来完成。

- IP核调用:Gowin软件提供了丰富的IP核资源(如PLL、存储器、接口IP等),可以通过图形化配置快速生成高性能模块,极大提升开发效率。

第3步:逻辑综合

点击“Synthesis”按钮或运行相应流程。综合器将HDL代码翻译优化成由基本逻辑门、触发器、存储器等组成的门级网表。此阶段会检查语法和基本逻辑错误。

第4步:约束输入

这是保证设计在物理硬件上正确运行的必要环节。主要是通过编辑“.cst”约束文件来定义:

- 引脚约束:将设计中的输入/输出信号分配到FPGA芯片的具体物理引脚上,必须与开发板原理图一致。

- 时序约束:定义时钟频率、输入延迟、输出延迟等,指导布局布线器优化以实现时序收敛。

第5步:布局布线

点击“Place & Route”按钮。该步骤将综合后的网表“放置”到FPGA芯片内部的特定逻辑单元(如查找表LUT、寄存器)中,并在这些单元之间进行物理“连线”。软件会努力满足你的时序约束。

第6步:生成编程文件

布局布线成功后,运行“Generate Bitstream”。该过程会生成最终的可下载到FPGA的比特流文件(通常是.fs或.bit格式)。

第7步:下载与调试

使用高云编程器(或其他兼容下载器)连接开发板与电脑。

在软件中打开“Program Device”工具,加载生成的比特流文件,将其烧录至FPGA。

观察开发板上的现象,验证功能。

若功能不符,需返回第2步进行调试。强烈建议利用 Gowin在线逻辑分析仪(GLA) 进行内部信号抓取,这是定位问题最有效的手段之一。

四、新手实践建议

- 从官方例程开始:高云软件和开发板通常附带丰富的示例工程,先运行一个最简单的LED闪烁例程,走通整个流程。

- 重视约束文件:引脚分配错误是新手最常见的导致“不工作”的原因,务必仔细核对。

- 善用GLA调试:比起盲目修改代码,用GLA观察实际信号能更快定位问题所在。

- 查阅官方文档:高云官网提供的《用户指南》、《数据手册》和《IP核手册》是解决问题的最佳参考资料。

五、

掌握Gowin云源软件的基本操作和FPGA开发的标准流程,是开启高云FPGA设计之旅的第一步。这个过程看似步骤繁多,但熟练后便会形成肌肉记忆。下一期,我们将通过一个具体的实战项目——例如UART通信或PWM控制——来将本期的理论知识付诸实践。

(注:本文基于特定版本软件撰写,实际操作请以您使用软件的具体版本和官方最新文档为准。)

如若转载,请注明出处:http://www.leiyuninfo.com/product/48.html

更新时间:2026-04-16 12:26:37